#### **Master Thesis**

Technical

Czech

University

in Prague

**F**3

Faculty of Electrical Engineering Department of Measurement

# Learning and automation GPIO platform

Ondřej Hruška

Supervisor: doc. Ing. Radislav Šmíd, Ph.D. Field of study: Cybernetics and Robotics Subfield: Sensors and Instrumentation 2018

# MASTER'S THESIS ASSIGNMENT

#### I. Personal and study details

| Student's name:      | Hruška Ondřej                     | Personal ID number: | 420010 |

|----------------------|-----------------------------------|---------------------|--------|

| Faculty / Institute: | Faculty of Electrical Engineering |                     |        |

| Department / Institu | ute: Department of Measurement    |                     |        |

| Study program:       | Cybernetics and Robotics          |                     |        |

| Branch of study:     | Sensors and Instrumentation       |                     |        |

#### II. Master's thesis details

Master's thesis title in English:

Learning and Automation GPIO Platform

Master's thesis title in Czech:

Výuková a automatizační GPIO platforma

#### Guidelines:

Design and implement a modular system consisting of a motherboard and additional modules for connecting sensors, actuators and general inputs via I2C, SPI, UART, 1-Wire or other interfaces to the central system via USB, UART, and wireless interfaces. Allow access to built-in processor peripherals such as ADC, DAC, and timers (PWM, frequency measurement). Design a comfortable way to set the configuration without firmware changes. For the designed system, create a service library in C, Python, and MATLAB.

Bibliography / sources:

[1] STMicroelectronics datasheets, http://www.st.com

[2] Ganssle, J.: The Art of Designing Embedded Systems, Elsevier Science, 2008.

[3] Chi, Qingping & Yan, Hairong & Zhang, Chuan & Pang, Zhibo & Da Xu, Li. (2014).: A Reconfigurable Smart Sensor Interface for Industrial WSN in IoT Environment. Industrial Informatics, IEEE Transactions on. 10. 1417-1425. 10.1109/TII.2014.2306798.

Name and workplace of master's thesis supervisor:

doc. Ing. Radislav Šmíd, Ph.D., Department of Measurement, FEL

Name and workplace of second master's thesis supervisor or consultant:

Date of master's thesis assignment: 10.01.2018

Deadline for master's thesis submission:

Assignment valid until: by the end of summer semester 2018/2019

doc. Ing. Radislav Šmíd, Ph.D. Supervisor's signature

Head of department's signature

prof. Ing. Pavel Ripka, CSc. Dean's signature

#### III. Assignment receipt

The student acknowledges that the master's thesis is an individual work. The student must produce his thesis without the assistance of others, with the exception of provided consultations. Within the master's thesis, the author must state the names of consultants and include a list of references.

Date of assignment receipt

Student's signature

CVUT-CZ-ZDP-2015.1

© ČVUT v Praze, Design: ČVUT v Praze, VIC

# Declaration

Prohlašuji, že jsem předloženou práci vypracoval samostatně a že jsem uvedl veškeré použité informační zdroje v souladu s Metodickým pokynem o dodržování etických principů při přípravě vysokoškolských závěrečných prací.

V Praze, 27. května 2018

.....

# Acknowledgements

blabla

# Abstract

This thesis documents the development of a general purpose software and hardware platform for interfacing low level hardware from high level programming languages and applications run on a PC, using USB and also wirelessly.

The requirements of common engineering tasks and problems occurring in the university environment were evaluated to design an extensible, reconfigurable hardware module that would make a practical, versatile, and low cost tool that in some cases also eliminates the need for professional measurement and testing equipment.

Several hardware prototypes and control libraries in programming languages C and Python have been developed. The Python library additionally integrates with MATLAB scripts. The devices provide access to a range of hardware buses and low level features and can be reconfigured using configuration files stored inside its permanent memory.

#### Keywords:

Supervisor: doc. Ing. Radislav Šmíd, Ph.D.

## Abstrakt

Tato práce popisuje vývoj univerzální softwarové a hardwarové platformy pro přístup k hardwarovým sběrnicím a elektrickým obvodům z prostředí vysokoúrovňových programovacích jazyků a aplikací běžících na PC, a to za využití USB a také bezdrátově.

Byly vyhodnoceny požadavky typických problémů, vyskytujících se v praxi při práci s vestavěnými systémy a ve výuce, pro návrh snadno rozšiřitelného a přenastavitleného hardwarového modulu který bude praktickým, pohodlným a dostupným nástrojem který navíc v některých případech může nahradit profesionální laboratorní přístroje.

Bylo navrženo několik prototypů hardwarových modulů, spolu s obslužnými knihovnami v jazycích C a Python; k modulu lze také přistupovat z prostředí MATLAB. Přístroj umožňuje přístup k většině běžných hardwarových sběrnic a umožňuje také např. měřit frekvenci a vzorkovat či generovat analogové signály.

#### Klíčová slova:

Překlad názvu: Výuková a automatizační GPIO platforma

# Contents

### Part I Introduction

| 1   | Motivation                             | 3  |

|-----|----------------------------------------|----|

| 1.  | 1 The Project's Expected Outcome       | 4  |

| 2   | Requirement Analysis                   | 7  |

|     | 2.0.1 Interfacing Intelligent Modules  | 7  |

|     | 2.0.2 Analog Signal Acquisition        | 7  |

|     | 2.0.3 Analog Signal Output             | 8  |

|     | 2.0.4 Logic Level Input and Output     | 8  |

|     | 2.0.5 Pulse Generation and Measurement | 8  |

| 2.2 | 1 Connection to the Host Computer      | 8  |

|     | 2.1.1 Messaging                        | 8  |

|     | 2.1.2 Configuration Files              | 9  |

| 2.2 | 2 Planned Feature List                 | 9  |

| 2.3 | 3 Microcontroller Selection            | 10 |

| 2.4 | 4 Form Factor Considerations           | 10 |

| 3   | Existing Solutions                     | 13 |

| 3.1 | 1 Bus Pirate                           | 13 |

| 3.2 | 2 Raspberry Pi                         | 14 |

| 3.3 | 3 Professional DAQ Modules             | 14 |

| 3.4 | 4 The Firmata Protocol                 | 15 |

### Part II Theoretical Background

| 4 Universal Serial Bus 1                     | 19 |

|----------------------------------------------|----|

| 4.1 Basic Principles and Terminology 2       | 20 |

| 4.2 USB Physical Layer                       | 23 |

| 4.3 USB Classes                              | 23 |

| 4.3.1 Mass Storage Class                     | 24 |

| 4.3.2 CDC/ACM Class                          | 24 |

| 4.3.3 Interface Association: Composite Class | 25 |

| 5 FreeRTOS                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 5.1 Basic FreeRTOS Concepts and Functions                                                                                                                                                                                                                                                                                                                            | 27                                                                                                                     |

| 5.1.1 Tasks                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                                                     |

| 5.1.2 Synchronization Objects                                                                                                                                                                                                                                                                                                                                        | 28                                                                                                                     |

| 6 The FAT16 File System and Its Emulation                                                                                                                                                                                                                                                                                                                            | 29                                                                                                                     |

| 6.1 The General Structure of the FAT File System                                                                                                                                                                                                                                                                                                                     | 29                                                                                                                     |

| 6.1.1 Boot Sector                                                                                                                                                                                                                                                                                                                                                    | 30                                                                                                                     |

| 6.1.2 File Allocation Table                                                                                                                                                                                                                                                                                                                                          | 30                                                                                                                     |

| 6.1.3 Root Directory                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                                                     |

| 6.2 FAT16 Emulation                                                                                                                                                                                                                                                                                                                                                  | 32                                                                                                                     |

| 6.2.1 Handling a Read Access                                                                                                                                                                                                                                                                                                                                         | 32                                                                                                                     |

| 6.2.2 Handling a Write Access                                                                                                                                                                                                                                                                                                                                        | 33                                                                                                                     |

| 6.2.3 File Name Change                                                                                                                                                                                                                                                                                                                                               | 33                                                                                                                     |

| 6.2.4 File Creation                                                                                                                                                                                                                                                                                                                                                  | 33                                                                                                                     |

| 6.2.5 File Content Change                                                                                                                                                                                                                                                                                                                                            | 34                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                        |

| 7 Supported Hardware Buses                                                                                                                                                                                                                                                                                                                                           | 35                                                                                                                     |

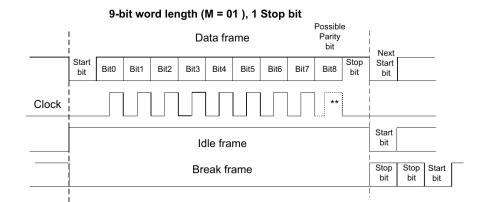

| <ul><li>7 Supported Hardware Buses</li><li>7.1 UART and USART</li></ul>                                                                                                                                                                                                                                                                                              | <b>35</b><br>35                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                        |

| 7.1 UART and USART                                                                                                                                                                                                                                                                                                                                                   | 35                                                                                                                     |

| 7.1 UART and USART       7.1.1 Examples of Devices Using UART                                                                                                                                                                                                                                                                                                        | 35<br>35                                                                                                               |

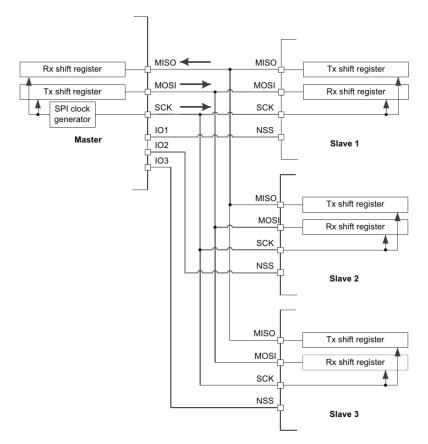

| 7.1 UART and USART         7.1.1 Examples of Devices Using UART         7.2 SPI                                                                                                                                                                                                                                                                                      | 35<br>35<br>36                                                                                                         |

| <ul> <li>7.1 UART and USART</li> <li>7.1.1 Examples of Devices Using UART</li> <li>7.2 SPI</li> <li>7.2.1 Examples of Devices Using SPI</li> </ul>                                                                                                                                                                                                                   | 35<br>35<br>36<br>36                                                                                                   |

| <ul> <li>7.1 UART and USART</li> <li>7.1.1 Examples of Devices Using UART</li> <li>7.2 SPI</li></ul>                                                                                                                                                                                                                                                                 | 35<br>35<br>36<br>36<br>37                                                                                             |

| <ul> <li>7.1 UART and USART</li> <li>7.1.1 Examples of Devices Using UART</li> <li>7.2 SPI</li> <li>7.2.1 Examples of Devices Using SPI</li> <li>7.3 I2C</li> <li>7.3.1 Examples of Devices Using I2C</li> </ul>                                                                                                                                                     | 35<br>35<br>36<br>36<br>37<br>38                                                                                       |

| 7.1 UART and USART7.1.1 Examples of Devices Using UART7.2 SPI7.2.1 Examples of Devices Using SPI7.3 I2C7.3.1 Examples of Devices Using I2C7.4 1-Wire                                                                                                                                                                                                                 | 35<br>35<br>36<br>36<br>37<br>38<br>38                                                                                 |

| <ul> <li>7.1 UART and USART</li></ul>                                                                                                                                                                                                                                                                                                                                | 35<br>35<br>36<br>37<br>38<br>38<br>38<br>39                                                                           |

| 7.1 UART and USART         7.1.1 Examples of Devices Using UART         7.2 SPI         7.2.1 Examples of Devices Using SPI         7.3 I2C         7.3.1 Examples of Devices Using I2C         7.4 1-Wire         7.4.1 Examples of Devices Using 1-Wire         7.5 NeoPixel                                                                                       | <ol> <li>35</li> <li>35</li> <li>36</li> <li>36</li> <li>37</li> <li>38</li> <li>38</li> <li>39</li> <li>39</li> </ol> |

| <ul> <li>7.1 UART and USART</li> <li>7.1.1 Examples of Devices Using UART</li> <li>7.2 SPI</li> <li>7.2.1 Examples of Devices Using SPI</li> <li>7.3 I2C</li> <li>7.3.1 Examples of Devices Using I2C</li> <li>7.4 1-Wire</li> <li>7.4.1 Examples of Devices Using 1-Wire</li> <li>7.5 NeoPixel</li> </ul> 8 Additional Hardware Functions                           | <ol> <li>35</li> <li>36</li> <li>36</li> <li>37</li> <li>38</li> <li>38</li> <li>39</li> <li>39</li> <li>43</li> </ol> |

| <ul> <li>7.1 UART and USART</li> <li>7.1.1 Examples of Devices Using UART</li> <li>7.2 SPI</li> <li>7.2.1 Examples of Devices Using SPI</li> <li>7.3 I2C</li> <li>7.3.1 Examples of Devices Using I2C</li> <li>7.4 1-Wire</li> <li>7.4.1 Examples of Devices Using 1-Wire</li> <li>7.5 NeoPixel</li> </ul> 8 Additional Hardware Functions 8.1 Frequency Measurement | <ol> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>38</li> <li>39</li> <li>39</li> <li>43</li> </ol> |

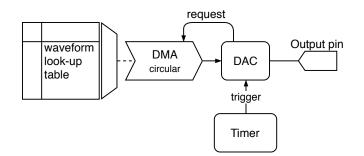

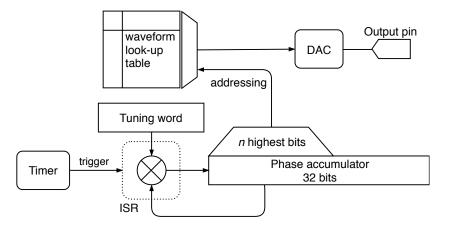

| 8.3.2 Direct Digital Synthesis | 46 |

|--------------------------------|----|

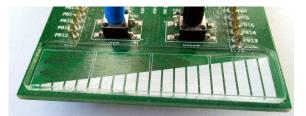

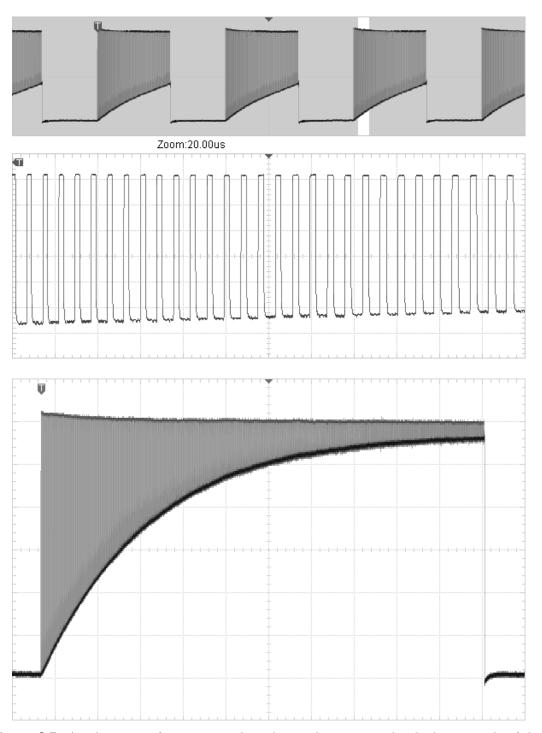

| 8.4 Touch Sensing              | 47 |

### Part III Implementation

| 9 Application Structure                              | 53 |

|------------------------------------------------------|----|

| 9.1 User's View of GEX                               | 53 |

| 9.2 Functions of the Core Framework                  | 54 |

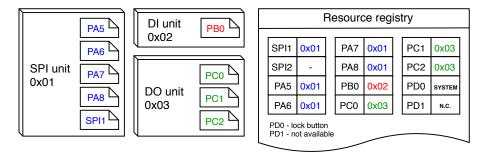

| 9.3 Resource Allocation                              | 55 |

| 9.4 Settings Storage                                 | 55 |

| 9.5 Functional Blocks                                | 56 |

| 9.6 Source Code Layout                               | 57 |

| 9.7 Communication Ports                              | 57 |

| 9.7.1 USB Connection                                 | 58 |

| 9.7.2 Communication UART                             | 58 |

| 9.7.3 Wireless Connection                            | 58 |

| 9.8 Message Passing                                  | 58 |

| 9.9 Interrupt Routing                                | 59 |

| 10 Communication Protocol                            | 61 |

| 10.1 Frame Structure                                 | 61 |

| 10.2 Message Listeners                               | 62 |

| 10.3 Designated Frame Types in GEX                   | 62 |

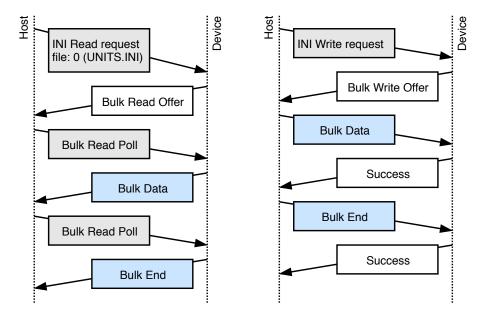

| 10.4 Bulk Read and Write Transactions                | 63 |

| 10.4.1 Bulk Read                                     | 63 |

| 10.4.2 Bulk Write                                    | 64 |

| 10.4.3 Persisting the Changed Configuration to Flash | 64 |

| 10.5 Reading a List of Units                         | 65 |

| 10.6 Unit Requests and Reports                       | 65 |

| 10.6.1 Unit Requests                                 | 65 |

| 10.6.2 Unit Reports                                  | 66 |

| 11 Wireless Interface                                | 67 |

| 11.1 Comparing SX1276 vs. nRF24L01+                  | 67 |

| 11.2 Integration of the nRF24L01+ into GEX $\dots$ | 68 |

|----------------------------------------------------|----|

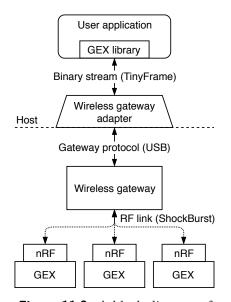

| 11.2.1 The Wireless Gateway Protocol               | 69 |

| 12 Units Overview and API                          | 71 |

| 12.1 Naming Conventions and Common Principles      | 71 |

| 12.1.1 Unit Naming                                 | 71 |

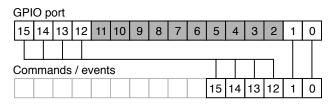

| 12.1.2 Packed Pin Access                           | 71 |

| 12.2 Digital Output                                | 72 |

| 12.2.1 Digital Output Configuration                | 72 |

| 12.2.2 Digital Output Events                       | 72 |

| 12.2.3 Digital Output Commands                     | 73 |

| 12.3 Digital Input                                 | 73 |

| 12.3.1 Digital Input Configuration                 | 73 |

| 12.3.2 Digital Input Events                        | 74 |

| 12.3.3 Digital Input Commands                      | 74 |

| 12.4 SIPO (Shift Register) Unit                    | 74 |

| 12.4.1 SIPO Configuration                          | 75 |

| 12.4.2 SIPO Commands                               | 75 |

| 12.5 NeoPixel Unit                                 | 75 |

| 12.5.1 NeoPixel Configuration                      | 76 |

| 12.5.2 NeoPixel Commands                           | 76 |

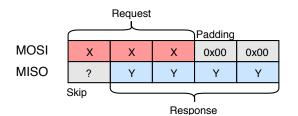

| 12.6 SPI Unit                                      | 76 |

| 12.6.1 SPI Configuration                           | 77 |

| 12.6.2 SPI Commands                                | 78 |

| 12.7 I2C Unit                                      | 78 |

| 12.7.1 I2C Configuration                           | 78 |

| 12.7.2 I2C Commands                                | 79 |

| 12.8 USART Unit                                    | 79 |

| 12.8.1 USART Configuration                         | 79 |

| 12.8.2 USART Events                                | 80 |

| 12.8.3 USART Commands                              | 81 |

| 12.9 1-Wire Unit                                   | 81 |

| 12.9.1 1-Wire Configuration             | 81 |

|-----------------------------------------|----|

| 12.9.2 1-Wire Events                    | 81 |

| 12.9.3 1-Wire Commands                  | 82 |

| 12.10 Frequency Capture Unit            | 82 |

| 12.10.1 Value Conversion Formulas       | 83 |

| 12.10.2 Frequency Capture Configuration | 83 |

| 12.10.3 Frequency Capture Commands      | 84 |

| 12.11 ADC Unit                          | 86 |

| 12.12 DAC Unit                          | 86 |

| 12.13 PWM Unit                          | 86 |

| 12.14 Touch Sensing Unit                | 86 |

## Appendices

# **Figures**

| 1.1 A collection of intelligent sensors and devices                                | 3  |

|------------------------------------------------------------------------------------|----|

| 1.2 An early sketch of a universal bench device                                    | 4  |

| 2.1 A Discovery board with STM32F072                                               | 11 |

| 2.2 Form factor sketches                                                           | 11 |

| 3.1 Bus Pirate v.4 (picture by Seeed Studio)                                       | 13 |

| 3.2 Raspberry Pi 2 (picture by Raspberry Pi Foundation)                            | 14 |

| 3.3 Professional tools that GEX can replace                                        | 15 |

| 4.1 USB hierarchical structure                                                     | 19 |

| 4.2 A detailed view of the host-device connection (USB specification rev. 1.1)     | 20 |

| 4.3 USB descriptors of a GEX prototype obtained using lsusb -vd vid:pid            | 22 |

| 4.4 NRZI encoding example                                                          | 23 |

| 4.5 USB pull-ups                                                                   | 24 |

| 6.1 An example of the GEX virtual file system                                      | 31 |

| 7.1 UART frame structure                                                           | 36 |

| 7.2 SPI master with multiple slaves                                                | 37 |

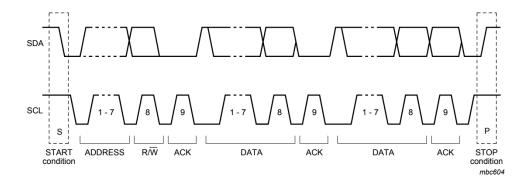

| 7.3 I2C message diagram                                                            | 39 |

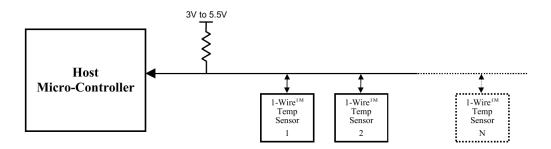

| 7.4 1-Wire topology (by <i>Dallas Semiconductor</i> )                              | 39 |

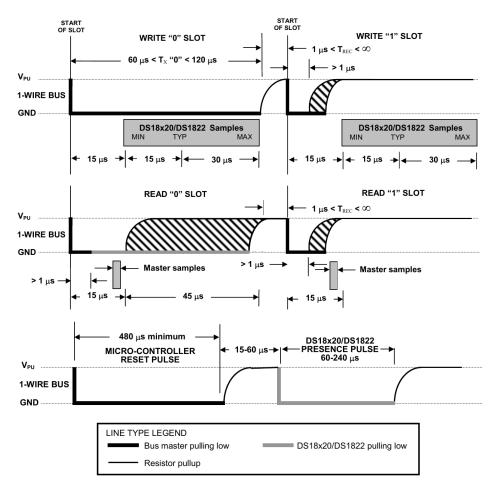

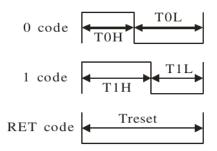

| 7.5 The 1-Wire DIO pulse timing (by <i>Dallas Semiconductor</i> )                  | 40 |

| 7.6 A close-up photo of the WS2812B package, showing the LED driver IC             | 41 |

| 7.7 NeoPixel pulse timing diagram and time constraints table ( $WS2812$ datasheet) | 41 |

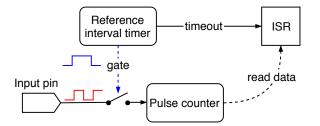

| 8.1 Direct frequency measurement method                                            | 44 |

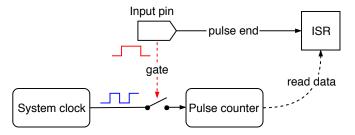

| 8.2 Reciprocal frequency measurement method                                        | 44 |

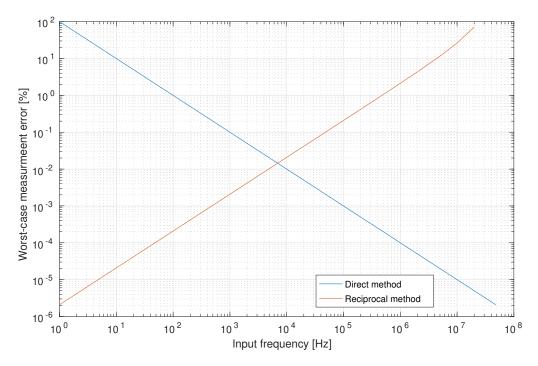

| 8.3 Frequency measurement methods comparison                                       | 45 |

| 8.4 A simple implementation of the waveform generator                              | 46 |

| 8.5 A block diagram of a direct digital synthesis waveform generator               | 47 |

| 8.6 The touch slider on a STM32F072 Discovery board                                | 48 |

| 8.7 A voltage waveform measured on the touch sensing pad. The bottom side of the envelope equals the sampling capacitor's voltage—this is the phase where both capacitors are connected. The detailed view (middle) shows the individual charging cycles. The bottom screenshot captures the entire waveform after the analog | r  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| comparator was disabled                                                                                                                                                                                                                                                                                                       | 49 |

| 9.1 An example allocation in the resource registry                                                                                                                                                                                                                                                                            | 55 |

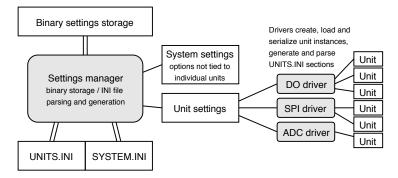

| 9.2 Structure of the settings subsystem                                                                                                                                                                                                                                                                                       | 56 |

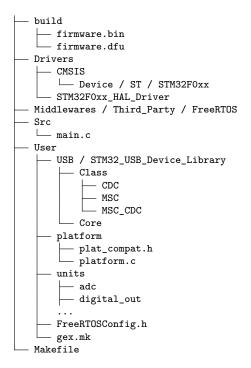

| 9.3 The general structure of the source code repository                                                                                                                                                                                                                                                                       | 57 |

| 10.1 A diagram of the bulk read and write transaction                                                                                                                                                                                                                                                                         | 64 |

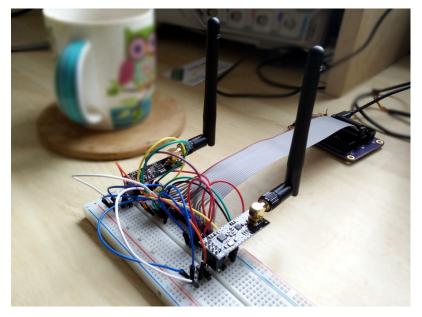

| 11.1 Test setup with a GEX prototype controlling two nRF24L01+ modules $\ldots$                                                                                                                                                                                                                                               | 67 |

| 11.2 A block diagram of the wireless connection                                                                                                                                                                                                                                                                               | 69 |

| 12.1 Pin packing                                                                                                                                                                                                                                                                                                              | 71 |

| 12.2 SPI transaction using the QUERY command                                                                                                                                                                                                                                                                                  | 77 |

# Part I

# Introduction

# Chapter 1

## **Motivation**

Prototyping, design evaluation and the measurement of physical properties in experiments make a daily occurrence in the engineering praxis. Those tasks typically involve the generation and sampling of electrical signals coming to and from sensors, actuators, and other circuitry.

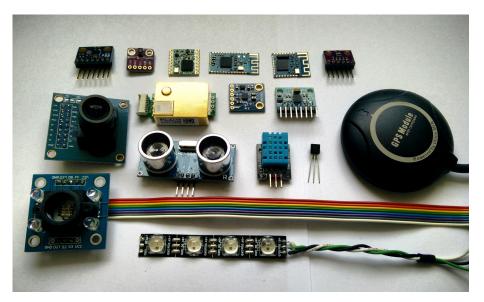

In the recent years a wide range of intelligent sensors became available thanks to the drive for miniaturization in the consumer electronics industry. Those devices often provide a sufficient accuracy and precision while keeping the circuit complexity and cost low. In contrast to analog sensors, here the signal conditioning and processing circuits are built into the sensor itself and we access it using a digital connection.

**Figure 1.1:** A collection of intelligent sensors and devices, most on breadboard adapters: (from top left) a waveform generator, a gesture detector, a LoRa and two Bluetooth modules, an air quality and pressure sensor, a  $CO_2$  sensor, a digital compass, an accelerometer, a GPS module, a camera, an ultrasonic range finder, a humidity sensor, a 1-Wire thermometer, a color detector and an RGB LED strip.

To conduct experiments with those integrated modules, or even just familiarize ourselves with a device before using it in a project, we need a way to easily interact with them. It's also convenient to have a direct access to hardware, be it analog signal sampling, generation, or even just logic level inputs and outputs. However, the drive for miniaturization and the advent of USB (Universal Serial Bus) lead to the disappearance of low level computer ports, such as the printer port (LPT), that would provide an easy way of doing so.

Today, when one wants to perform measurements using a digital sensor, the usual route is to implement an embedded firmware for a microcontroller that connects to the PC through USB, or perhaps just shows the results on a display. This approach has its advantages, but is time-consuming and requires knowledge entirely unrelated to the measurements we wish to perform. It would be advantageous to have a way to interface hardware without having to burden ourselves with the technicalities of the connection, even at the cost of lower performance compared to a specialized device or a professional tool.

The design and implementation of such a universal instrument is the object of this work. For technical reasons, such as naming the source code repositories, we need a name for the project; it'll be hereafter called *GEX*, a name originating from "GPIO Expander".

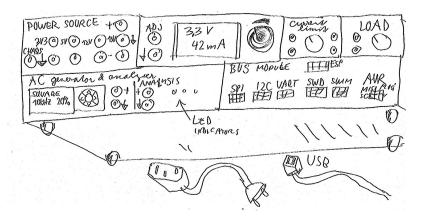

### **1.1** The Project's Expected Outcome

It's been a desire of the author to create an universal instrument connecting low level hardware to a computer for many years, and with this project it is finally being realized. Several related projects approaching this problem from different angles can be found on the internet; those will be presented in chapter 3. This project should not end with yet another tinkering tool that will be produced in a few prototypes and then forgotten. By building an extensible, open-source platform, GEX can become the foundation for future projects which others can expand, re-use and adapt to their specific needs.

**Figure 1.2:** An early (2016) sketch of a universal bench device including a power supply, electronic load, a signal generator and a bus module. The bottom half of the panel is in a large part implemented by GEX.

Building on the experience with earlier embedded projects, a STM32 microcontroller shall be used. Those are ARM Cortex M devices with a wide range of hardware peripherals that appear be a good fit for the project. Low-cost evaluation boards are widely available that could be used as a hardware platform instead of developing a custom PCB. In addition, those chips are relatively cheap and popular in the embedded hardware community; there's a good possibility of the project building a community around it and growing beyond what will be presented in this paper.

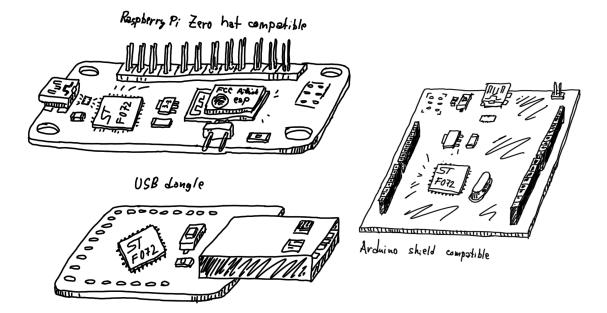

Besides the use of existing development boards, custom PCBs will be developed in different form factors. Those could use the Arduino connector or the Raspberry Pi Zero GPIO header (and board shape) to exploit the cases and boxes available for the minicomputer on the market, as well as add-on boards (*shields* and *HATs*).

The possibilities of wireless connection should be evaluated. This feature should make GEX useful e.g. in mobile robotics or when installed in poorly accessible locations.

# Chapter 2

# **Requirement Analysis**

We'll now investigate some situations where GEX could be used, to establish its requirements and desired features.

#### 2.0.1 Interfacing Intelligent Modules

When adding a new digital sensor or a module to a hardware project, we want to test it first, learn how to properly communicate with it and confirm its performance. Based on this evaluation we decide whether the module matches our expectations and learn how to properly connect it, which is needed for a successful PCB layout.

In experimental setups, this may be the only thing we need. Data can readily be collected after just connecting the module to a PC, same as commanding motor controllers or other intelligent devices.

A couple well known hardware buses have established themselves as the standard ways to interface digital sensors and modules: SPI, I2C and UART are the most used ones, often accompanied by a few extra GPIO lines such as Reset, Chip Enable, Interrupt. There are exceptions where silicon vendors have developed proprietary communication protocols that are still used, either for historical reasons or because of their specific advantages. An example is the 1-Wire protocol used by digital thermometers.

Moving to industrial and automotive environments, we can encounter various fieldbuses, Ethernet, CAN, current loop, HART, LIN, DALI, RS485 (e.g. Modbus), mbus, PLCBUS and others. Those typically use transceiver ICs and other circuitry, such as TVS, discrete filters, galvanic isolation etc. They could be supported using add-on boards and additional firmware modules handling the protocol. For simplicity and to meet time constraints, the development of those boards and modules will be left for future expansions of the project.

#### 2.0.2 Analog Signal Acquisition

Sometimes it's necessary to use a traditional analog sensor, capture a transient waveform or to just measure a voltage. GEX was meant to focus on digital interfaces, however giving it this capability makes it much more versatile. Nearly all microcontrollers include an analog-digital converter which we can use to measure input voltages and, paired with a timer, to records signals varying in time.

Certain tasks, such as capturing transient effects on a thermocouple when inserted into a flame (an example from developing fire-proof materials) demand level triggering similar 2. Requirement Analysis

to that of oscilloscopes. The converter continuously measures the input voltage and a timed capture starts only after a set threshold is exceeded. This can be accompanied by a pre-trigger feature where the timed capture is continuously running and the last sample is always compared with the threshold, recording a portion of the historic records together with the following samples.

#### 2.0.3 Analog Signal Output

An analog signal can not only be measured, but it's often necessary to also generate it. This could serve as an excitation signal for an experiment, for instance to measure the characteristic curves of a diode or a transistor. Conveniently, we can at the same time use GEX's analog input to record the output.

Generating an analog signal is possible using a pulse-width modulation (PWM) or by a dedicated digital-analog converter included in many microcontrollers. Higher frequencies or resolution can be achieved with a dedicated external IC.

#### 2.0.4 Logic Level Input and Output

We've covered some more advanced features, but skipped the simplest feature: a direct access to GPIO pins. Considering the latencies of USB and the PC's operating system, this can't be reliably used for "bit banging", however we can still accomplish a lot with just changing logic levels - e.g. to control character LCDs, or emulate some interfaces that include a clock line, like SPI. As mentioned in 2.0.1, many digital sensors and modules use plain GPIOs in addition to the communication bus for out-of-band signaling or features like chip selection or reset.

#### 2.0.5 Pulse Generation and Measurement

Some sensors have a variable frequency or a pulse-width modulated (PWM) output. To capture those signals and convert them to a more useful digital value, we can use the external input functions of a timer/counter in the microcontroller. Those timers have many possible configurations and can also be used for pulse counting or a pulse train generation.

### 2.1 Connection to the Host Computer

#### 2.1.1 Messaging

USB shall be the primary way of connecting the module to a host PC. Thanks to USB's flexibility, it can present itself as any kind of device or even multiple devices at once.

The most straightforward method of interfacing the board is by passing binary messages in a fashion similar to USART (and plain UART can be available as well). We'll need a duplex connection to enable command confirmations, query-type commands and asynchronous event reporting. This is possible either using a "Virtual COM port" driver (the CDC/ACM USB class), or through a raw access to the corresponding USB endpoints. Using a raw access avoids potential problems with the operating system's driver interfering or not recognizing the device correctly; on the other hand, having GEX appear as a serial port makes it easier to integrate into existing platforms that have a good serial port support (such as National Instruments LabWindows CVI or MATLAB).

A wireless attachment is also planned; after establishing a connection, the two-way link should work in a similar manner to UART or USB.

link to where this is better explained

#### 2.1.2 Configuration Files

The module must be easily reconfigurable. Given the settings are almost always going to be tied on the connected external hardware, it would be practical to have an option to store them permanently in the microcontroller's non-volatile memory.

We can load those settings into GEX using the serial interface, which also makes it possible to reconfigure it remotely when the wireless connection is used. With USB, we can additionally make the board appear as a mass storage device and expose the configuration as text files. This approach, inspired by ARM mbed's mechanism for flashing firmware images to development kits, avoids the need to create a configuration GUI, instead using the PC OS's built-in applications like File Explorer and Notepad. We can expose additional information, such as a README file with instructions or a pin-out reference, as separate files on the virtual disk.

### 2.2 Planned Feature List

Let's list the features we wish to initially support in the GEX firmware:

- Hardware interfacing functions

- I/O pin direct access (read, write), pin change interrupt

- Analog input: voltage measurement, sampled capture

- Analog output: static level, waveform generation

- Frequency, duty cycle, pulse length measurement

- Single pulse and PWM generation

- SPI, I<sup>2</sup>C, UART/USART

- Dallas 1-Wire

- NeoPixel (addressable LED strips)

- Communication with the host computer

- USB connection as virtual serial port or direct endpoint access

#### 2. Requirement Analysis

- Connection using plain UART

- Wireless attachment

#### • Configuration

- Fully reconfigurable, temporarily or permanently

- Settings stored in INI files

- File access through the communication API or using a virtual mass storage

### 2.3 Microcontroller Selection

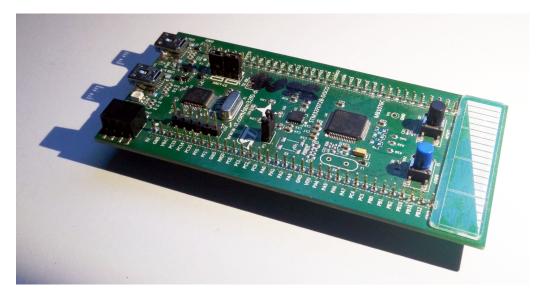

The STM32F072 microcontroller was chosen for the built prototypes and the initial firmware, owning to it's low cost, advanced peripherals and the availability of development boards. GEX can be later ported to other MCUs, like the STM32L072, STM32F103 or STM32F303.

The STM32F072 is a Cortex M0 device with 128 KiB of flash memory, 16 KiB of RAM and running at 48 MHz. It is equipped with a USB Full Speed peripheral block, a 12-bit ADC and DAC, a number of general purpose timers/counters, SPI, I<sup>2</sup>C, and USART peripherals, among others. It supports crystal-less USB, using the USB SOF packet for synchronization of the internal 48 MHz RC oscillator; naturally, a real crystal resonator will provide better timing accuracy.

To effectively utilize the time available for this work, only the STM32F072 firmware will be developed while making sure the planned expansion is as straightforward as possible.

### 2.4 Form Factor Considerations

It was mentioned in 1.1 that, while the GEX firmware can be used with existing evaluation boards from ST Microelectronics (figure 2.1), we wish to design and realize a few custom hardware prototypes that will be smaller, more convenient to use and hopefully also cheaper. Three possible form factors are drawn in figure 2.2.

Several factors play a role when deciding what the GEX PCB should look like:

The device must be comfortable and easy to use, which affects the choice of the USB connector, also with respect to cable availability: USB type A is not suitable for desktop computers where it would have to be plugged in the rear of the computer or in the front panel, but it may be usable with laptops; USB Mini-B and Micro-B connectors are both a popular choice in existing kits (e.g. Discovery and Nucleo boards), but Micro-B has a higher rated number of insertions and the cables are ubiquitous thanks to their use in mobile phones, therefore this appears to be the better connector choice.

link to the insertion count spec

The PCB size should be kept minimal to save manufacturing costs. When a standard connector shape and a pin assignment are used we gain the ability to install existing add-on boards designed for other platforms, like the Arduino or Raspberry Pi. Lastly, when the entire board shape is copied from an existing commercial product for which we can buy official or after-market cases, we get an easy access to cases without having to design them ourselves. This is the case of the Raspberry Pi Zero form factor.

Figure 2.1: A Discovery board with STM32F072 that can be used to run the GEX firmware

**Figure 2.2:** A sketch of three possible form factors for the GEX hardware prototype. Note the ESP8266 module which was considered as an option for wireless access but was eventually not used due to it's high current usage, unsuitable for battery operation.

# Chapter 3

# **Existing Solutions**

The idea of making it easier to interact with low level hardware from a PC is not new. Several solutions to this problem have been developed, each with its own advantages and drawbacks. Some examples will be presented in this chapter.

#### 3.1 **Bus Pirate**

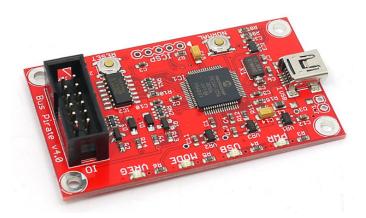

Figure 3.1: Bus Pirate v.4 (picture by Seeed Studio)

#### link to pic source page

Bus Pirate, developed by Ian Lesnet at Dangerous Prototypes and manufactured by disk Seeed Studio, is a USB-attached device providing access to hardware interfaces like SPL I<sup>2</sup>C, USART and 1-Wire, as well as frequency measurement and direct pin access.

link

The board aims to make it easy for users to familiarize themselves with new chips and modules; it also provides a range of programming interfaces for flashing microcontroller firmwares and memories. It communicates with the PC using a FTDI USB-serial bridge.

Bus Pirate is open source and in scope it's similar to GEX. It can be scripted and controlled from languages like Python or Perl, connects to USB and provides a good selection of hardware interfaces.

The board is based on a PIC16 microcontroller running at 32 MHz. Its analog/digital converter (ADC) only has a resolution of 10 bits (1024 levels). There is no digital/analog 3. Existing Solutions

converter (DAC) available on the chip, making applications that require a varied output voltage more difficult. Another limitation of the board is its low number of GPIO pins which may be insufficient for certain applications. The Bus Pirate, at the time of writing, can be purchased for a price similar to some Raspberry Pi models.

### 3.2 Raspberry Pi

Figure 3.2: Raspberry Pi 2 (picture by Raspberry Pi Foundation)

The Raspberry Pi's GPIO header, which can be directly controlled by user applications, was one of the primary inspirations behind GEX. It can be controlled using C and Python (among others) and offers general purpose IØ, SPI, I2C, UART and PWM, with other protocols being easy to emulate thanks to the high speed of the system processor.

The Raspberry Pi is commonly used in schools as a low-cost PC alternative that encourage students' interest in electronics, programming and science. The board is often built into more permanent projects that make use of its powerful processor, such as wildlife camera traps or home automation projects.

The Raspberry Pi could be used for the same quick evaluations or experiments we want to perform with GEX, however they would either have to be performed directly on the mini-computer itself with attached monitor and keyboard, or use some form of remote access (e.g. SSH). When we have a more powerful computer available, a USB device like GEX would be more convenient.

### **3.3** Professional DAQ Modules

Various professional tools that would fulfill our needs exist on the market, but their high price makes them inaccessible for users with a limited budget, such as hobbyists or students who would like to keep such a device for personal use. An example is the National Instruments (NI) "I<sup>2</sup>C/SPI Interface Device" which also includes several GPIO lines, the NI USB DAQ module, or some of the Total Phase I<sup>2</sup>C/SPI gadgets (figure 3.3). The performance GEX can provide may not always match that of those professional tools, but in many cases it'll be a sufficient substitute at a fraction of the cost.

(a) : NI I<sup>2</sup>C/SPI Interface Device

(b) : NI USB DAQ module

(c) : Total Phase SPI/I<sup>2</sup>C Host "Aardwark"

**Figure 3.3:** An example of professional tools that GEX could replace in less demanding scenarios (pictures taken from marketing materials)

### **3.4 The Firmata Protocol**

#### links

Firmata is a communication protocol based on MIDI (*Musical Instrument Digital Interface*) for passing data to and from embedded microcontrollers. MIDI is mainly used for attaching electronic musical instruments, such as synthesizers, keyboards, mixers etc., to each other or to a PC. Firmata was designed for Arduino as a high level abstraction for its connection to the PC, typically using a FTDI chip or equivalent.

Implementing Firmata in the GEX firmware would make it possible to use existing Firmata libraries on the PC side. However, the protocol is limited by the encompassing MIDI format and isn't very flexible.

# Part II

# **Theoretical Background**

# Chapter 4

# **Universal Serial Bus**

This chapter presents an overview of the Universal Serial Bus (USB) Full Speed interface, with focus on the features used in the GEX firmware. USB is a versatile but complex interface, thus explaining it in its entirety is beyond the scope of this text. References to external material which explains the protocol in greater detail will be provided where appropriate.

add

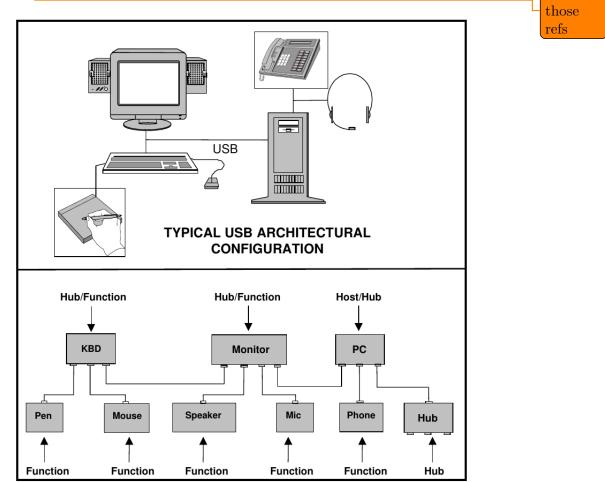

**Figure 4.1:** A diagram from the USB specification rev. 1.1 showing the hierarchical structure of the USB bus; The PC (Host) controls the bus and initiates all transactions.

4. Universal Serial Bus

## 4.1 Basic Principles and Terminology

#### review and correct inaccuracies

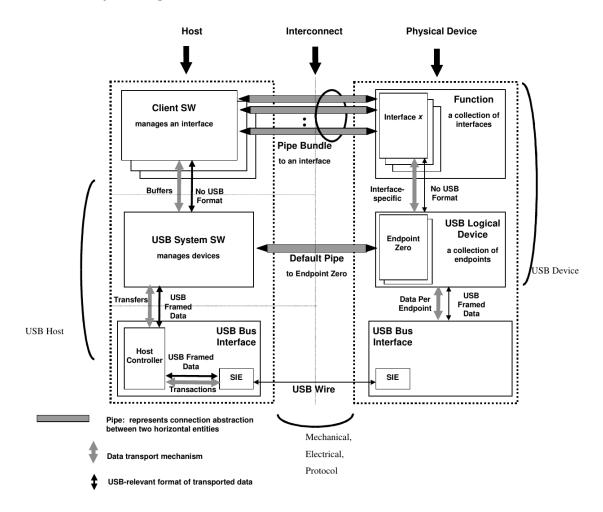

USB is a hierarchical bus with a single master (host) and multiple slave devices. A USB device that provides functionality to the host is called a *function*. Communication between the host and a function is organized into virtual channels called *pipes*. Each pipe is identified by an *endpoint* number.

Figure 4.2: A detailed view of the host-device connection (USB specification rev. 1.1)

Endpoints can be either unidirectional or bidirectional; the direction from the host to a function is called OUT, the other direction (function the host) is called IN. A bidirectional endpoint is technically composed of a IN and OUT endpoint with the same number. All transactions (both IN and OUT) are initiated by the host; functions have to wait for their turn. Endpoint 0 is bidirectional, always enabled, and serves as a *control endpoint*. The host uses the control endpoint to read information about the device and configure it as needed.

There are four types of transfers: control, bulk, isochronous, and interrupt. Each endpoint is configured for a fixed transfer type.

- *Control* initial configuration after device plug-in; also used for other aplication-specific control messages that can affect other pipes.

- *Bulk* used for burst transfers of large messages, commonly e.g. for mass storage devices

- *Isochronous* streaming with guaranteed low latency; designed for audio or video streams where some data loss is preferred over stuttering

- *Interrupt* low latency short messages, used for human interface devices like mice and keyboards

The endpoint transfer type and other characteristics, together with other information about the device, such as the serial number, are defined in a *descriptor table*. This is a tree-like binary structure defined in the function's memory. The descriptor table is loaded by the host to learn about the used endpoints and to attach the right driver to it.

The function's endpoints are grouped into *interfaces*. An interface describes a logical connection of endpoints, such as the reception and transmission endpoint that belong together. An interface is assigned a *class* defining how it should be used. Standard classes are defined by the USB specification to provide a uniform way of interfacing devices of the same type, such as human-interface devices (mice, keyboards, gamepads) or mass storage devices. The use of standard classes makes it possible to re-use the same driver software for devices from different manufacturers. The class used for the GEX's "virtual COM port" function was originally meant for telephone modems, a common way of connecting to the Internet at the time the first versions of USB were developed. A device using this class will show as /dev/ttyACM0 on Linux and as a COM port on Windows, provided the system supports it natively or the right driver is installed.

add reference to the document

4. Universal Serial Bus

| Device Decemintory               |                              | Intonfoco Decerintory |          |                     |

|----------------------------------|------------------------------|-----------------------|----------|---------------------|

| Device Descriptor:<br>bLength 18 | 3                            | Interface Descriptor: | 9        |                     |

| 0                                |                              | bLength               | 9<br>4   |                     |

| 1 51                             |                              | bDescriptorType       |          |                     |

|                                  | 9 Miscellaneous Device       | bInterfaceNumber      | 1<br>0   |                     |

|                                  |                              | bAlternateSetting     |          |                     |

|                                  |                              | bNumEndpoints         | 1        |                     |

|                                  | l Interface Association      | bInterfaceClass       |          | mmunications        |

| bMaxPacketSize0 64               | -                            | bInterfaceSubClass    |          | stract (modem)      |

|                                  | 3 STMicroelectronics         | bInterfaceProtocol    |          | -commands (v.25ter) |

| idProduct 0x572a                 |                              | iInterface            | 5 V1     | rtual Comport ACM   |

| bcdDevice 0.01                   |                              | CDC Header:           |          |                     |

|                                  | l MightyPork                 | bcdCDC                | 1.10     |                     |

|                                  | 2 GEX                        | CDC Call Management:  |          |                     |

|                                  | 3 0029002F-42365711-32353530 | bmCapabilities        | 0x00     |                     |

| bNumConfigurations 1             |                              | bDataInterface        | 2        |                     |

| Configuration Descriptor:        |                              | CDC ACM:              |          |                     |

| bLength                          | 9                            | bmCapabilities        | 0x06     |                     |

| bDescriptorType                  | 2                            | sends break           |          |                     |

| wTotalLength                     | 98                           | line coding and       | serial s | tate                |

| bNumInterfaces                   | 3                            | CDC Union:            |          |                     |

| bConfigurationValue              | 1                            | bMasterInterface      | 1        |                     |

| iConfiguration                   | 0                            | bSlaveInterface       | 2        |                     |

|                                  | x80                          | Endpoint Descriptor:  |          |                     |

| (Bus Powered)                    |                              | bLength               | 7        |                     |

|                                  | 500mA                        | bDescriptorType       | 5        |                     |

| Interface Descriptor:            | _                            | bEndpointAddress      | 0x83     | EP 3 IN             |

| bLength                          | 9                            | bmAttributes          | 3        |                     |

| bDescriptorType                  | 4                            | Transfer Type         |          | Interrupt           |

| bInterfaceNumber                 | 0                            | Synch Type            |          | None                |

| bAlternateSetting                | 0                            | Usage Type            |          | Data                |

| bNumEndpoints                    | 2                            | wMaxPacketSize        | 0x0008   | 1x 8 bytes          |

| bInterfaceClass                  | 8 Mass Storage               | bInterval             | 255      |                     |

| bInterfaceSubClass               | 6 SCSI                       | Interface Descriptor: |          |                     |

| bInterfaceProtocol               | 80 Bulk-Only                 | bLength               | 9        |                     |

| iInterface                       | 4 Settings VFS               | bDescriptorType       | 4        |                     |

| Endpoint Descriptor:             |                              | bInterfaceNumber      | 2        |                     |

| bLength                          | 7                            | bAlternateSetting     | 0        |                     |

| bDescriptorType                  | 5                            | bNumEndpoints         | 2        |                     |

| bEndpointAddress                 | Ox81 EP 1 IN                 | bInterfaceClass       |          | C Data              |

| bmAttributes                     | 2                            | bInterfaceSubClass    | 0        |                     |

| Transfer Type                    | Bulk                         | bInterfaceProtocol    | 0        |                     |

| Synch Type                       | None                         | iInterface            |          | rtual Comport CDC   |

| Usage Type                       | Data                         | Endpoint Descriptor:  |          |                     |

| wMaxPacketSize                   | 0x0040 1x 64 bytes           | bLength               | 7        |                     |

| bInterval                        | 0                            | bDescriptorType       | 5        |                     |

| Endpoint Descriptor:             |                              | bEndpointAddress      |          | EP 2 OUT            |

| bLength                          | 7                            | bmAttributes          | 2        |                     |

| bDescriptorType                  | 5                            | Transfer Type         |          | Bulk                |

| bEndpointAddress                 | Ox01 EP 1 OUT                | Synch Type            |          | None                |

| bmAttributes                     | 2                            | Usage Type            |          | Data                |

| Transfer Type                    | Bulk                         | wMaxPacketSize        | 0x0040   | 1x 64 bytes         |

| Synch Type                       | None                         | bInterval             | 0        |                     |

| Usage Type                       | Data                         | Endpoint Descriptor:  |          |                     |

| wMaxPacketSize                   | 0x0040 1x 64 bytes           | bLength               | 7        |                     |

| bInterval                        | 0                            | bDescriptorType       | 5        | ED O IN             |

| Interface Association:           | 0                            | bEndpointAddress      | 0x82     | EP 2 IN             |

| bLength                          | 8                            | bmAttributes          | 2        | D11-                |

| bDescriptorType                  | 11                           | Transfer Type         |          | Bulk                |

| bFirstInterface                  | 1                            | Synch Type            |          | None                |

| bInterfaceCount                  | 2                            | Usage Type            | 00040    | Data                |

| bFunctionClass                   | 2 Communications             | wMaxPacketSize        | 0x0040   | 1x 64 bytes         |

| bFunctionSubClass                | 2 Abstract (modem)           | bInterval             | 0        |                     |

| bFunctionProtocol                | 1 AT-commands (v.25ter)      |                       |          |                     |

| iFunction                        | 5 Virtual Comport ACM        |                       |          |                     |

. . . .

Figure 4.3: USB descriptors of a GEX prototype obtained using lsusb -vd vid:pid

### 4.2 USB Physical Layer

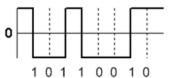

USB uses differential signaling with NRZI encoding (*Non Return to Zero Inverted*, fig. 4.4) and bit stuffing. The encoding, together with frame formatting, checksum verification, retransmission, and other low level aspects of the USB connection are entirely handled by the USB block in the microcontroller's silicon; normally we do not need to worry about those details. What needs more attention are the electrical characteristics of the bus, which need to be understood correctly for a successful schematic and PCB design.

The USB cable contains 4 conductors:

- $V_{BUS}$  (+5 V)

- D+

- D-

- Ground

Figure 4.4: NRZI encoding example

The data lines, D+ and D-, are also commonly labeled DP and DM. This differential pair should be routed in parallel and kept at approximately the same length.

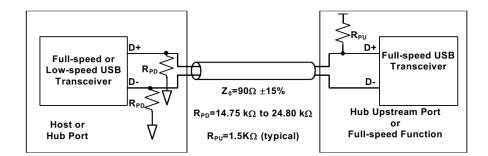

USB revisions are, where possible, backwards compatible, often even keeping the same connector shape. The bus speed is negotiated by the device using a  $1.5 \text{ k}\Omega$  pull-up resistor to 3.3 V on one of the data lines: for Full Speed, D+ is pulled high (fig. 4.5), for Low Speed it's on D–. The polarity of the differential signals is inverted depending on the used speed. Some microcontrollers integrate the correct pull-up resistor inside the USB block (including out STM32F072), removing the need for an external resistor.

When a function wants to be re-enumerated by the host, which is needed to reload the descriptors and re-attach the correct drivers, it can momentarily remove the pull-up resistor, which the host will interpret as if the device was plugged out. With an internal pull-up this can be done by flipping a bit in a control register. An external resistor can be connected through a transistor controlled by a GPIO pin.

```

https://www.eevblog.com/forum/projects/driving-the-1k5-usb-pull-up-resistor-on-d/

```

http://www.beyondlogic.org/usbnutshell/usb2.shtml

The  $V_{BUS}$  line supplies power to *bus-powered* devices. *Self-powered* devices can leave this pin unconnected and instead use an external power supply. The maximal current drawn from the  $V_{BUS}$  line is configured using a descriptor and should not be exceeded, but experiments suggest this is often not enforced.

### 4.3 USB Classes

This section explains the Mass Storage class and the CDC/ACM class that are used in the GEX firmware. A list of all standard classes with a more detailed explanation can be found on the USB.org website at http://www.usb.org/developers/defined\_class.

#### 4. Universal Serial Bus

**Figure 4.5:** Pull-up and pull-down resistors of a Full Speed function, as prescribed by the USB specification rev. 2.0

#### 4.3.1 Mass Storage Class

The Mass Storage class (MSC) is supported by all modern operating systems (MS Windows, MacOS, GNU/Linux, FreeBSD etc.) to support thumb drives, external disks, memory card readers and other storage devices.

#### references

The MSC specification defines multiple transport protocols that can be selected using the descriptors. For it's simplicity, the Bulk Only Transport (BOT) will be used. BOT uses two bulk endpoints for reading and writing blocks of data and for the exchange of control commands and status messages. For the device to be recognized by the operating system, it must also implement a command set. Most mass storage devices use the SCSI Transparent command set <sup>1</sup>. The command set's commands let the host read information about the attached storage, such as its capacity, and check for media presence and readiness to write or detach. This is used e.g. for the "Safely Remove" function which checks that all internal buffers have been written to Flash.

#### links

The MSC class together with the SCSI command set are implemented in a USB Device library provided by ST Microelectronics. The library also includes a basic CDC/ACM implementation (see below).

In order to emulate a mass storage device without having a physical storage medium, we need to generate and parse the filesystem on-the-fly as the host OS tries to access it. This will be discussed in chapter 6.

### 4.3.2 CDC/ACM Class

Historically meant for modem communication, this class is now the de facto standard way of making USB devices appear as serial ports on the host OS. The CDC (*Communication Device Class*) uses three endpoints: bulk IN and OUT, and an interrupt endpoint.

<sup>&</sup>lt;sup>1</sup>To confirm this assertion, the descriptors of five thumb drives and an external hard disk were analyzed using lsusb. All but one device used the SCSI command set, one (the oldest thumb drive) used *SFF-8070i*. A list of possible command sets can be found in TODO (usb spec overview)

The interrupt endpoint is used for control commands and notifications while the bulk endpoints are used for useful data. ACM stands for *Abstract Control Model* and it's a CDC's subclass that defines the control messages format. Since we don't use a physical UART and the line is virtual both on the PC and in the end device, the control commands can be ignored.

verify this vvv

An interesting property of this class is that the bulk endpoints transport raw data without any wrapping frames. By changing the device class in the descriptor table to 255 (*Vendor Specific Class*), we can retain the messaging functionality of the designated endpoints and access the device directly using e.g. libUSB, while the OS will ignore it and won't try to attach any driver that could interfere otherwise. The same trick can be used to hide the mass storage class when not needed.

### 4.3.3 Interface Association: Composite Class

Since it's creation, the USB specification expected that each function will have only one interface enabled at a time. After it became apparent that there is a need for having multiple unrelated interfaces work in parallel, a workaround called the *Interface Association Descriptor* (IAD) was introduced. IAD is an entry in the descriptor table that defines which interfaces belong together and should be handled by the same software driver.

To use the IAD, the function's class must be set to 239 (EFh), subclass 2 and protocol 1, so the OS knows to look for the presence of IADs before binding drivers to any interfaces.

In GEX, the IAD is used to tie together the CDC and ACM interfaces while leaving out the MSC interface which should be handled by a different driver. To make this work, a new *composite class* had to be created as a wrapper for the library-provided MSC and CDC/ACM implementations.

### Chapter 5

### **FreeRTOS**

FreeRTOS is a free, open-source real time operating system kernel that has been ported to over 30 microcontroller architectures. The kernel provides a scheduler and implements queues, semaphores and mutexes that are used for message passing between concurrent tasks and for synchronization. FreeRTOS is compact designed to be easy to understand; it's written in C with the exception of some architecture-specific routines that use assembly.

FreeRTOS is used in GEX for its synchronization objects and queues that make it easy to safely pass messages from USB interrupts to a working thread that processes them and sends back responses. Similar mechanism is used to handle external interrupts.

### 5.1 Basic FreeRTOS Concepts and Functions

#### 5.1.1 Tasks

Threads in FreeRTOS are called *tasks*. Each task is assigned a memory area to use as its stack space, and a structure with it's name, saved context and other metadata used by the kernel. A context includes the program counter, stack pointer and other register values. Task switching is done by saving and restoring this context by manipulating the values on stack before leaving and interrupt.

At start-up the firmware initializes the kernel, registers tasks to run and starts the scheduler. From this point onward the scheduler is in control and runs the tasks using a round robin scheme. Which task should run is primarily determined by their priority numbers, but there are other factors. FreeRTOS supports both static and dynamic object creation, including registering new tasks at run-time.

#### Task Run States

Tasks can be in one of four states: Suspended, Ready, Blocked, Running. The Suspended state does not normally occur in a task's life cycle, it's entered and left using API calls on demand. A task is in the Ready state when it can run, but is currently paused because a higher priority task is running. It enters the Running state when the scheduler switches to it. A Running task can wait for a synchronization object (e.g. a mutex) to be available. At this point it enters a Blocked state and the scheduler runs the next Ready task. When no tasks can run, the Idle Task takes control; it can either enter a sleep state to save power, or wait in an infinite loop until another task is available.

#### 5. FreeRTOS

#### Task Switching and Interrupts

Task switching occurs periodically in a SysTick interrupt, usually every 1 ms. After one tick of run time, the running task is paused (enters Ready state), or continues to run if no higher priority task is available. If a high priority task waits for an object and this is made available in an interrupt, the previously running task is paused and the waiting task is resumed immediately (enters the Running state).

Only a subset of the FreeRTOS API can be accessed from interrupt routines, for example it's not possible to use the delay function or wait for an object with a timeout, because the SysTick interrupt which increments the tick counter has the lowest priority and couldn't run. This is by design to prevent unexpected context switching in nested interrupts.

FreeRTOS uses a *priority inheritance* mechanism to prevent situations where a high priority task waits for an object held by a lower priority task (called *priority inversion*). The blocking task's priority is temporarily raised to the level of the blocked high priority task so it can finish faster and release the held object. Its priority is then degraded back to the original value. When the lower priority task itself is blocked, the same process can be repeated.

#### 5.1.2 Synchronization Objects

FreeRTOS provides binary and counting semaphores, mutexes and queues.

Binary semaphores can be used for task notifications, e.g. a task waits for a semaphore to be set by an interrupt when a byte is received on the serial port. This makes the task Ready and if it has a higher priority than the previously running task, it's immediately resumed to process the event.

Counting semaphores are used to represent available resources. A pool of resources (e.g. DMA channels) is accompanied by a counting semaphore, so that tasks can wait for a resource to become available in the pool and then subtract the semaphore value. After finishing with a resource, the semaphore is incremented again and another task can use it.

Mutexes, unlike semaphores, must be taken and released in the same thread (task). They're used to guard exclusive access to a resource, such as transmitting on the serial port. When a mutex is taken, a task that wishes to use it enters Blocked state and is resumed once the mutex becomes available and it can take it.

Queues are used for passing messages between tasks, or from interrupts to tasks. Both sending and receiving queue messages can block until the operation becomes possible.

In GEX, mutexes and semaphores are used for sending messages to the PC, and a queue is used for processing received bytes and to send messages from interrupts, because it's not possible to block on a mutex or semaphore while inside an interrupt routine.

### Chapter 6

### The FAT16 File System and Its Emulation

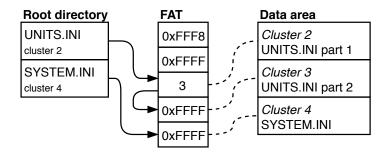

A file system (FS) is used by GEX to provide a comfortable access to the configuration files. By emulating a Mass Storage USB device, the module appears as a thumb drive on the host PC, and the user can edit its configuration using their preferred text editor. The FAT16 file system was selected for its simplicity and a good cross-platform support.

Three variants of the FAT (File Allocation Table) file system exist: FAT12, FAT16, and FAT32. FAT12 was used on floppy disks and it is similar to FAT16, except for additional size constraints and a FAT entry packing scheme. FAT16 and FAT32 are FAT12's later developments from the time when hard disks became more common and the old addressing scheme couldn't support their larger capacity.

This chapter will explain the structure of FAT16 and the challenges faced when trying to emulate it without a physical data storage.

### **6.1** The General Structure of the FAT File System

The storage medium is organized into *sectors* (or *blocks*), usually 512 bytes long. Those are the smallest addressing unit in the disk structure. The disk starts with a *boot sector*, also called *master boot record* (MBR). That is followed by optional reserved sectors, one or two copies of the file allocation table, and the root directory. All disk areas are aligned to a sector boundary:

| Disk area        | Size / Notes                            |

|------------------|-----------------------------------------|

| Boot sector      | 1 sector                                |

| Reserved sectors | optional                                |

| FAT 1            | 1 or more sectors, depends on disk size |

| FAT 2            | optional, a back-up copy of FAT $1$     |

| Root directory   | 1 or more sectors                       |

| Data area        | Organized in <i>clusters</i>            |

Table 6.1: Areas of a FAT-formatted disk

#### 6.1.1 Boot Sector